# UNIVERSIDAD MICHOACANA DE SAN NICOLÁS DE HIDALGO

División de Estudios de Posgrado de La Facultad de Ingeniería Eléctrica

Nonlinear Analysis of Power Systems including FACTS and Custom Power Devices Based on Bifurcation Theory and Newton Methods

> by Juan Segundo Ramírez

## THESIS

Presented for the Degree of Doctor in Sciences in Electrical Engineering

> **Thesis Advisor** Dr. J. Aurelio Medina Ríos

MORELIA, MICHOACÁN

FEBRUARY 2010

# **Table of Contents**

| L   | LIST OF SYMBOLS AND ACRONYMS                                                  | V    |

|-----|-------------------------------------------------------------------------------|------|

| L   | LIST OF FIGURES                                                               | /III |

| I   | LIST OF TABLES                                                                | xv   |

|     | LIST OF PUBLICATIONS                                                          |      |

|     |                                                                               |      |

|     | ABSTRACTXV                                                                    |      |

| A   | ACKNOWLEDGMENT                                                                | ίX   |

| 1   | INTRODUCTION                                                                  | 1    |

|     | 1.1 STATE OF THE ART                                                          | 1    |

|     | 1.1.1 Static Compensator (STATCOM)                                            | 3    |

|     | 1.1.2 Static Synchronous Series Compensator (SSSC)                            | 3    |

|     | 1.1.3 Unified Power Flow Controller (UPFC)                                    |      |

|     | 1.1.4 Other FACTS Devices                                                     |      |

|     | 1.2 POWER ELECTRONIC APPLICATION IN DISTRIBUTION SYSTEMS                      | 8    |

|     | 1.2.1 Distribution Static Compensator (DSTATCOM)                              | 9    |

|     | 1.2.2 Dynamic Voltage Restorer (DVR)                                          |      |

|     | 1.2.3 Unified Power Quality Compensator (UPQC)                                | . 11 |

|     | 1.3 MOTIVATION BEHIND THE PRESENT RESEARCH                                    |      |

|     | 1.4 OBJECTIVES                                                                |      |

|     | 1.5 Methodology                                                               | . 13 |

|     | 1.6 CONTRIBUTIONS                                                             |      |

|     | 1.7 Thesis Outline                                                            |      |

| 2   | A GENERAL OVERVIEW OF POWER CONVERTERS EMPLOYED BY FACTS                      | S    |

| ANI | D CP DEVICES                                                                  | . 16 |

|     | 2.1 INTRODUCTION                                                              | . 16 |

|     | 2.2 INVERTER TOPOLOGY                                                         | . 17 |

|     | 2.2.1 Single-Phase H-bridge Inverter                                          | . 17 |

|     | 2.2.2 Three-Phase H-bridge Inverter                                           |      |

|     | 2.2.3 Three-Phase Inverter                                                    | . 25 |

|     | 2.2.4 Six-Pulse Voltage Source Converter                                      |      |

|     | 2.2.5 Sinusoidal Pulse Width Modulation (SPWM)                                |      |

|     | 2.3 SIMPLIFIED MODELS.                                                        |      |

|     | 2.3.1 Fundamental Frequency Component of the Switching Functions for the SPWM |      |

|     | 2.3.2 Simplified Representation of the Hysteresis Modulation Technique        |      |

|     | 2.4 CONCLUSIONS                                                               |      |

| 2   |                                                                               |      |

| 3   |                                                                               |      |

|     | 3.1 MODELING OF FACTS DEVICES BASED ON SPWM VSCs                              |      |

|     | 3.2 MODELING AND SIMULATION OF VSCs                                           | . 41 |

|     | 3.3 VSC STATE SPACE REPRESENTATION                                            |      |

|     | 3.4 SINUSOIDAL PULSE-WIDTH MODULATION CONVERTER REPRESENTATION                | . 42 |

|     | 3.4.1 Fourier Model                                                           | . 42 |

| 3.4.2      | Smooth Switching Function                                        | 46    |

|------------|------------------------------------------------------------------|-------|

| 3.5 \$     | SOLUTION COMPARISONS AND RESULTS VALIDATION                      | 49    |

| 3.5.1      | Static Compensator (STATCOM)                                     | 50    |

| 3.5.2      | Static Synchronous Series Compensator (SSSC)                     | 53    |

| 3.5.3      | Unified Power Flow Controller (UPFC)                             | 55    |

| 3.6 I      | DISTRIBUTION STATIC COMPENSATOR                                  | 56    |

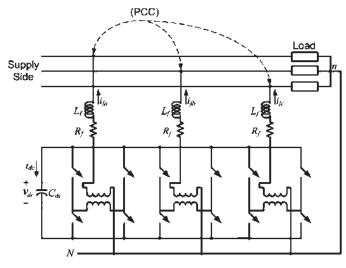

| 3.6.1      | Distribution Network including the DSTATCOM                      | 56    |

| 3.6.2      | DSTATCOM Operating in Current Control Mode                       | 59    |

|            | DSTATCOM Operating in Voltage Mode                               | 63    |

| 3.7 1      | DEAL SOURCE AND SMOOTH HYSTERESIS BAND APPROACH: COMPARATIVE     |       |

| ANALYSIS . |                                                                  |       |

| 3.7.1      | 1 0                                                              |       |

| 3.7.2      | DSTATCOM Operating in Voltage Mode                               |       |

|            | DYNAMIC VOLTAGE RESTORER                                         |       |

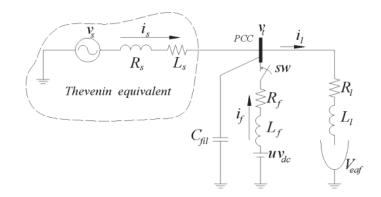

| 3.8.1      | 5 0                                                              |       |

| 3.8.2      | DVR Structure                                                    |       |

| 3.8.3      | Closed-Loop Compensation Algorithm                               |       |

| 3.8.4      | Test Case                                                        |       |

| 3.8.5      | Experimental Verification of the Fourier and Hyperbolic models   |       |

| 3.9 (      | CONCLUSIONS                                                      | 79    |

| 4 CONS     | STRUCTION OF PERIODIC SOLUTIONS                                  | 80    |

| 4.1        | INTRODUCTION                                                     | 80    |

|            | FAST TIME DOMAIN SOLUTION                                        |       |

|            | DISCRETE EXPONENTIAL EXPANSION METHOD                            |       |

| 4.3.1      |                                                                  |       |

| 4.3.2      | Identification of $\mathbf{\Phi}$                                |       |

| 4.3.3      | Incorporation of Sparsity                                        |       |

| 4.3.4      | Variants of the DEE Method                                       |       |

| 4.3.5      | Updating of the Transition Matrix $\Phi$                         |       |

| 4.3.6      | Computation of the Exponential Matrix                            |       |

| 4.3.7      | Simulation Results                                               | 86    |

| 4.4 I      | ENHANCED NUMERICAL DIFFERENTIATION METHOD                        | 91    |

| 4.4.1      | Simulation Results                                               | 92    |

| 4.5 0      | CONCLUSION                                                       | 96    |

| 5 STAB     | BILITY ANALYSIS BASED ON BIFURCATION THEORY OF THE               |       |

| DSTATCOM   | AND DVR                                                          | 98    |

| 5.1 0      | CONTINUATION TECHNIQUES AND BIFURCATION THEORY                   | 98    |

| 5.2 I      | DSTATCOM OPERATING IN CURRENT CONTROL MODE STABILITY ANALYSIS BA | 4SED  |

| ON BIFURC. | ATION THEORY                                                     | . 100 |

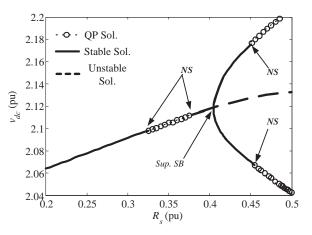

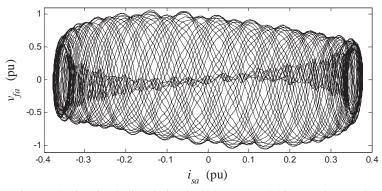

| 5.2.1      | Bifurcation Analysis for DSTATCOM in Current Control Mode        | . 100 |

| 5.3 1      | BIFURCATION ANALYSIS FOR DSTATCOM IN VOLTAGE CONTROL MODE        | . 107 |

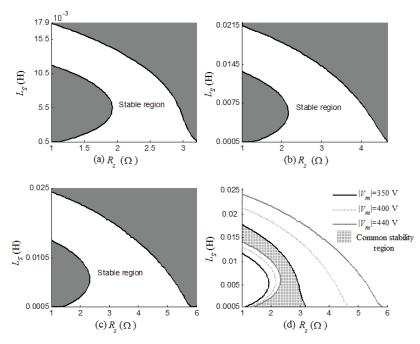

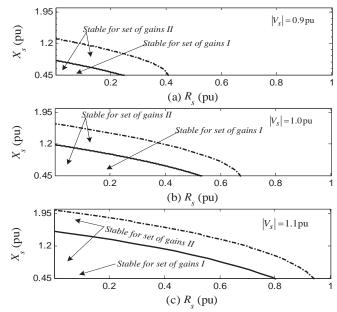

| 5.3.1      | Stability Regions in the $R_s$ - $L_s$ Plane                     | . 107 |

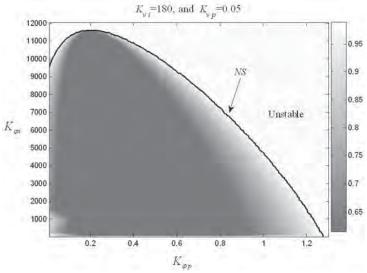

| 5.3.2      | Stability Regions in the Gains Plane                             |       |

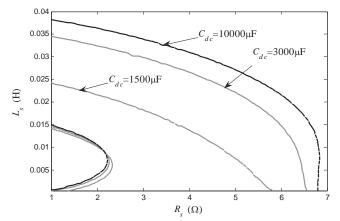

| 5.3.3      | dc Capacitor Impact on the Stability Region                      |       |

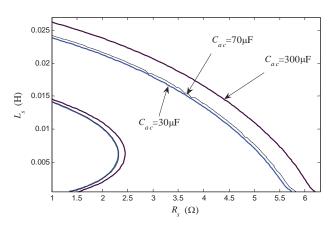

| 5.3.4      | ac Capacitor Filter Impact on the Stability Region               |       |

| 5.4 I      | DVR BIFURCATION ANALYSIS                                         |       |

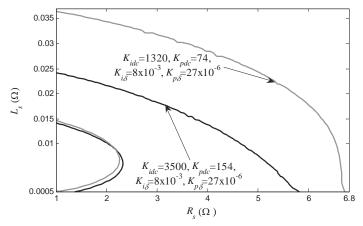

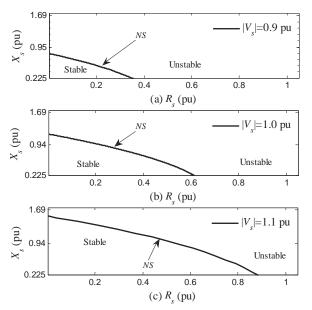

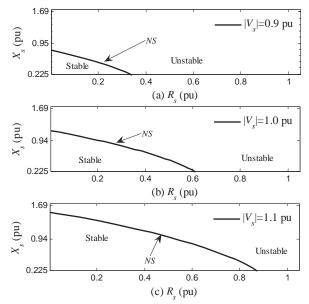

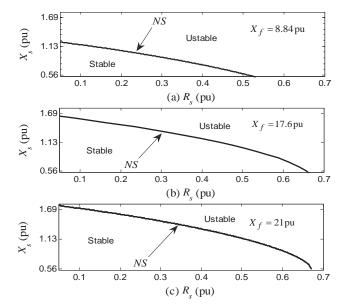

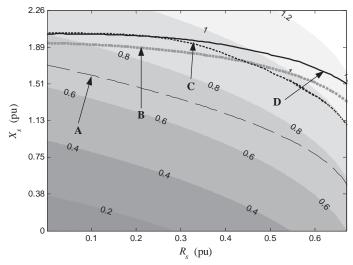

| 5.4.1      | Stability Regions in the $R_s - X_s$ Plane                       | . 115 |

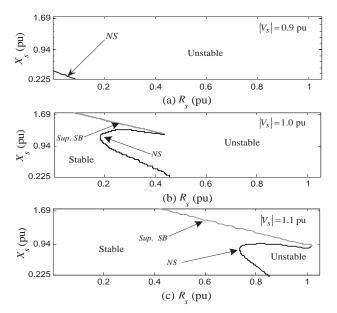

| 5.4.2      | Stability Regions in the Gains Plane                             |       |

| 5.4.3      | ac Capacitor Impact on the Stability                             |       |

|            |                                                                  |       |

| 5.4.4 dc Capacitor Impact on the Stability            |       |

|-------------------------------------------------------|-------|

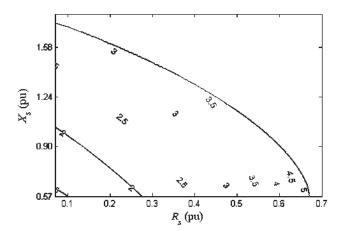

| 5.4.5 Feasible Solutions of the DVR                   | . 123 |

| 5.5 CONCLUSION                                        | . 125 |

| 6 CONCLUSION                                          | . 127 |

| 6.1 GENERAL CONCLUSIONS                               | . 127 |

| 6.2 RECOMMENDATIONS FOR FURTHER RESEARCH DEVELOPMENTS | . 128 |

| APPENDIX A                                            | . 130 |

| APPENDIX B                                            | . 135 |

| BIBLIOGRAPHY                                          | . 136 |

# **List of Symbols and Acronyms**

| ac capacitor                                                        | $C_{ac}$                       |

|---------------------------------------------------------------------|--------------------------------|

| Adjustable System Drive                                             | ASD                            |

| Amplitude modulation ratio                                          | $m_a$                          |

| Aprille and Trick Method                                            | AT                             |

| Average load power                                                  | $P_l^{av}$                     |

| Average voltage across the dc capacitor                             | $v_{dc}^{av}$                  |

| Brute Force                                                         | BF                             |

| Capacitance                                                         | С                              |

| Compensation voltage injected by the DVR                            | $oldsymbol{V}_{f}$             |

| Custom Power                                                        | CP                             |

| Cutoff Frequency                                                    | $\Omega_c$                     |

| dc capacitor                                                        | $C_{dc}$                       |

| Derivative respect to time of a function $\mathbf{f}(\mathbf{x},t)$ | $d\mathbf{f}(\mathbf{x},t)/dt$ |

| Direct Approach                                                     | DA                             |

| Direct axis                                                         | d                              |

| Discrete Exponential Expansion Method                               | DEE                            |

| Discrete transition matrix                                          | $\Phi_k$                       |

| Distribution Static Compensator                                     | DSTATCOM                       |

| Dynamic Voltage Regulator                                           | DVR                            |

| Electric Arc Furnace                                                | EAF                            |

| Electrical output torque                                            | $T_e$                          |

| Enhanced Numerical Differentiation Method                           | END                            |

| Exponential function                                                | е                              |

| Finite Differences Method                                           | FD                             |

| Fixed Capacitor                                                     | FC                             |

| Flexible ac Trasmission Systems                                     | FACTS                          |

| Flux linkage ( $i=q$ or $d$ and $j=s$ or $r$ )                      | λij                            |

| Fourth-order Runge-Kutta                                            | RK4                            |

| Frequency modulation ratio                                          | $m_f$                          |

| Fundamental component of $v_{tx}$ , for $x = a, b, c$               | $V_{tfx}$                      |

| High Voltage Direct Current Light                                   | HVDC Light                     |

| High Voltage Direct Current Transmission                            | HVDC                           |

| Hysteresis Band                                                     | h                              |

| Identity matrix                                                     | Ι                              |

| Inductance                                                          | L                              |

| Infinite                                                            | $\infty$                       |

| Instantaneous active power                                          | Р                              |

| Instantaneous current source                                        | $i_s$                          |

| Instantaneous current                                               | i                              |

| Instantaneous load current                                          | $i_l$                          |

| Instantaneous power losses                                          | $P_{loss}$                     |

| L                                                                   | 1000                           |

| Instantaneous reactive new or                                  | 0                                          |

|----------------------------------------------------------------|--------------------------------------------|

| Instantaneous reactive power                                   | Q                                          |

| Instantaneous terminal voltage                                 | V <sub>t</sub>                             |

| Instantaneous voltage source<br>Instantaneous voltage          | V <sub>s</sub>                             |

| Integral gain of the load voltage in the DVR                   | V<br>V                                     |

|                                                                | $K_{i \varphi}$                            |

| Integral gain of the power factor controller                   | $K_{ieta}$                                 |

| Integral gain of voltage controller of dc capacitor            | K <sub>idc</sub>                           |

| Integration operator                                           | ∫<br>∎(a)                                  |

| Jacobian                                                       | $\mathbf{J}(t)$                            |

| Load torque                                                    | $T_L$ (or $T_l$ )                          |

| Load voltage (phasor)                                          | $V_l$                                      |

| Load voltage magnitude                                         | $ V_l $                                    |

| Load voltage reference magnitude                               | $ V_l^{ref} $                              |

| Magnetic flux                                                  | λ                                          |

| Magnitude of the current source                                | $ I_S $                                    |

| Magnitude of the load current                                  | $ I_l $                                    |

| Magnitude of the terminal voltage                              | $ V_t $                                    |

| Magnitude of the voltage at the converter terminals of the DVR | $ V_{inj} $                                |

| Magnitude of the voltage source                                | $ V_{s} $                                  |

| Magnitude                                                      |                                            |

| Mismatch                                                       | Δ                                          |

| Moment of inertia                                              | J                                          |

| Number of Full Cycles                                          | NFC                                        |

| Number of poles                                                | р                                          |

| Numerical Differentiation Method                               | ND                                         |

| Ordinary Differential Equations                                | ODEs                                       |

| Period                                                         | Т                                          |

| Point Common Coupling                                          | PCC                                        |

| Proportional gain of the load voltage in the DVR               | $K_{p \varphi}$                            |

| Proportional gain of the power factor controller               | $K_{peta}$                                 |

| Proportional gain of voltage controller of dc capacitor        | $K_{pdc}$                                  |

| q and $d$ axis magnetizing flux linkages                       | $\lambda_{mq}, \lambda_{md}$ , espectively |

| q and $d$ axis rotor currents                                  | $i_{qr}$ , $i_{dr}$ , respectively         |

| q and $d$ axis rotor voltages                                  | $v_{qr}$ , $v_{qr}$ , respectively         |

| q and $d$ axis stator currents                                 | $i_{qs}$ , $i_{ds}$ , respectively         |

| q and $d$ axis stator voltages                                 | $v_{qs}$ , $v_{qs}$ , respectively         |

| Quadrature axis                                                | q                                          |

| Reference compensator currents                                 | $i_f^*$                                    |

| Reference dc voltage                                           | $v_{dc}^{*}$                               |

| Resistance                                                     | R                                          |

| Rotor angular electrical speed                                 | $\omega_r$                                 |

| Rotor axis                                                     | r                                          |

| Rotor leakage reactance ( $\omega_e L_{lr}$ )                  | $X_{lr}$                                   |

| Rotor resistance                                               | $R_r$                                      |

|                                                                |                                            |

| State variables at the beginning of the base cycle | $\mathbf{x}^{i}$      |

|----------------------------------------------------|-----------------------|

| State variables at the end of the base cycle       | $\mathbf{x}^{i+1}$    |

| State variables at the limit cycle                 | $\mathbf{x}^{\infty}$ |

| Static Synchronous Compensator                     | STATCOM               |

| Static Synchronous Series compensator              | SSSC                  |

| Static Var Compensator                             | SVC                   |

| Stator angular electrical base frequency           | $\omega_b$            |

| Stator angular electrical frequency                | $\omega_e$            |

| Stator axis                                        | S                     |

| Stator leakage reactance ( $\omega_e L_{ls}$ )     | $X_{ls}$              |

| Stator resistance                                  | $R_s$                 |

| Switching function                                 | S                     |

| Terminal voltage (phasor)                          | $oldsymbol{V}_t$      |

| Thyristor Controlled Reactors                      | TCR                   |

| Thyristor Controlled Series Compensator            | TCSC                  |

| Thyristor Switch Capacitor                         | TSC                   |

| Time                                               | t                     |

| Transition matrix                                  | Φ                     |

| Trapezoidal Rule                                   | TR                    |

| Unified Power Flow Controller                      | UPFC                  |

| Unified Power Quality Conditioner                  | UPQC                  |

| Voltage at the converter terminals of the DVR      | V <sub>inj</sub>      |

|                                                    |                       |

# **List of Figures**

| Figure 1.1 FACTS devices based on VSCs. (a) STATCOM, (b) SSSC, and (c) UPFC                             | 2            |

|---------------------------------------------------------------------------------------------------------|--------------|

| Figure 1.2 (a) Schematic diagram of a TSC, and (b) multiple TSC connection                              | 5            |

| Figure 1.3 Schematic diagram of a TCR                                                                   | 5            |

| Figure 1.4 Steady state voltage-current waveform of a TCR                                               | 5            |

| Figure 1.5 SVC connected to an ac network                                                               | 6            |

| Figure 1.6 Schematic Representation of a TCSC                                                           | 6            |

| Figure 1.7 Variation of TCSC reactance with the firing angle                                            | 7            |

| Figure 1.8 A double-poled Thyristor-Based HVDC Link                                                     | 7            |

| Figure 1.9 A VSC-Based HVDC Link                                                                        | 8            |

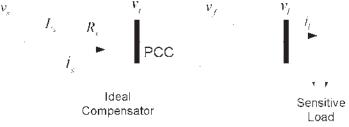

| Figure 1.10 Schematic diagram of load compensating using DSTATCOM                                       | 9            |

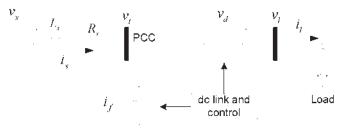

| Figure 1.11 Schematic diagram of voltage regulating using DSTATCOM                                      | 10           |

| Figure 1.12 Schematic diagram of voltage regulating using DVR                                           | 10           |

| Figure 1.13 Schematic representation of UPQC connected in a distribution system                         | 11           |

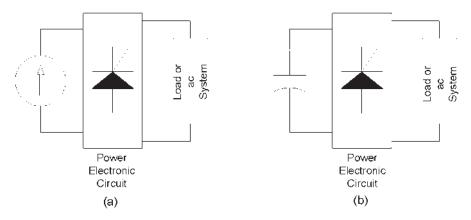

| Figure 2.1 Schematic representation of a (a) CSC and (b) VSC                                            | 17           |

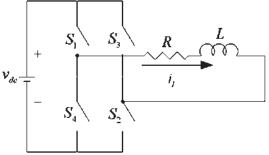

| Figure 2.2 Schematic diagram of a H-bridge inverter                                                     | 18           |

| <b>Figure 2.3</b> Equivalent circuits of the H-bridge inverter (a) when $S_1$ and $S_2$ are on, and (b) | ) when $S_3$ |

| and $S_4$ are on                                                                                        | 18           |

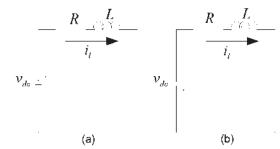

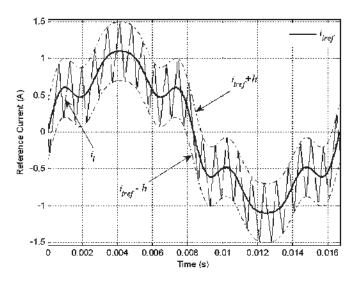

| Figure 2.4 Reference current and hysteresis band                                                        | 19           |

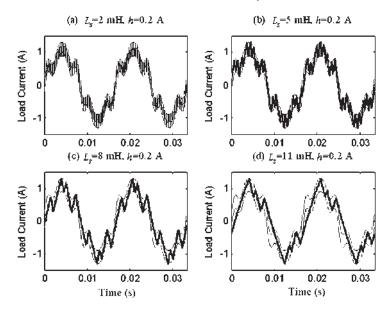

| Figure 2.5 Load current for various load inductors                                                      | 19           |

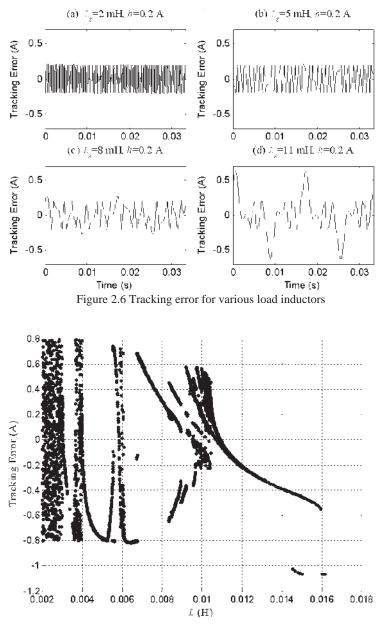

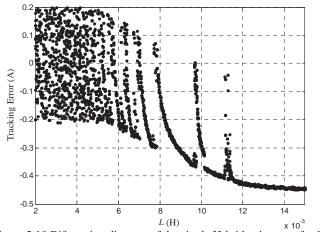

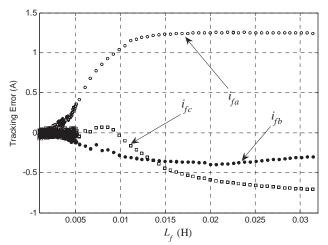

| Figure 2.6 Tracking error for various load inductors                                                    | 20           |

| Figure 2.7 Bifurcation diagram of the single H-bridge inverter for $h=0.8 A$                            | 20           |

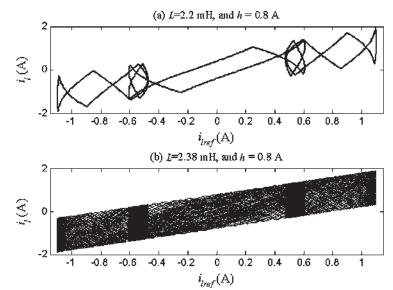

| <b>Figure 2.8</b> Phase portrait of $i_{ref} - I$ for (a) $L=2.2$ mH showing a 1T-periodic solution are | ıd for (b)   |

| L=2.28 mH showing a 34T-periodic solution                                                               | 21           |

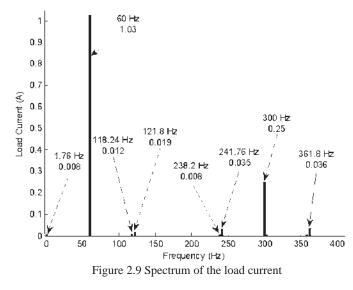

| Figure 2.9 Spectrum of the load current                                                                 | 21           |

| Figure 2.10 Bifurcation diagram of the single H-bridge inverter for $h=0.2 A$                           | 22           |

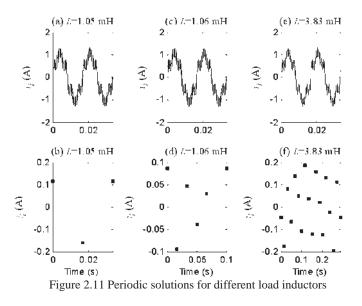

| Figure 2.11 Periodic solutions for different load inductors                                             | 22           |

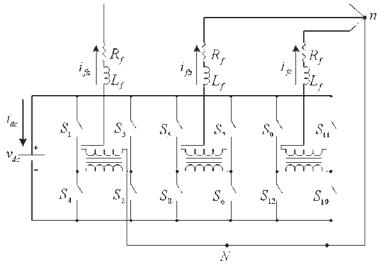

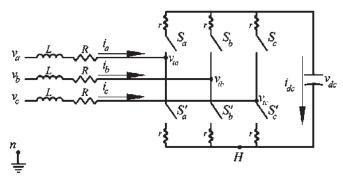

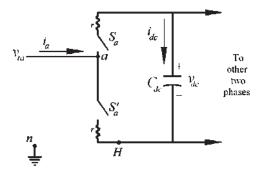

| Figure 2.12 Schematic diagram of a three-phase H-bridge inverter                                        | 23           |

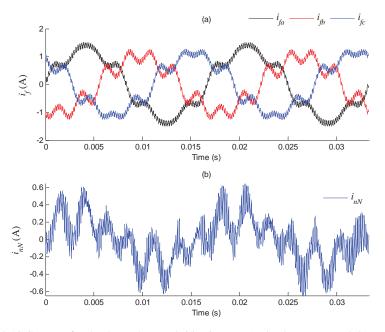

| Figure 2.13 Currents for the three-phase H-bridge inverter (a) load currents, and (b                    | ) neutral    |

| current                                                                                                 | 25           |

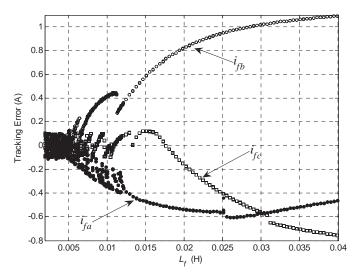

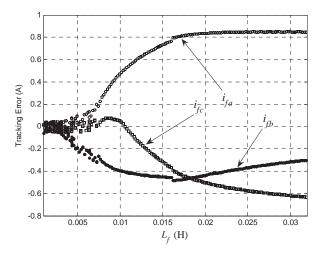

| Figure 2.14 Bifurcation diagram for the three-phase H-bridge inverter                                   | 25           |

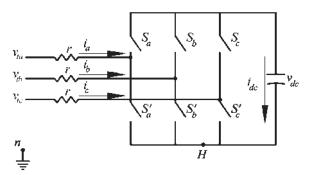

| Figure 2.15 Schematic diagram of a three-phase inverter                                                 |              |

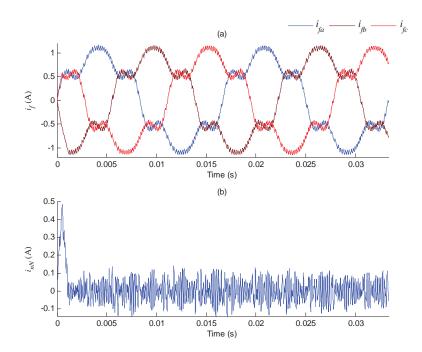

| Figure 2.16 Currents for the three-phase inverter (a) load currents, and (b) neutral current 28                         |

|-------------------------------------------------------------------------------------------------------------------------|

| Figure 2.17 Bifurcation diagram for the three-phase inverter: balanced case                                             |

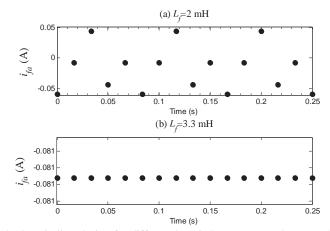

| <b>Figure 2.18</b> <i>Periodic solution for different load inductors (a)</i> $L_f = 2  mH$ , and (b) $L_f = 3.3  mH$ 29 |

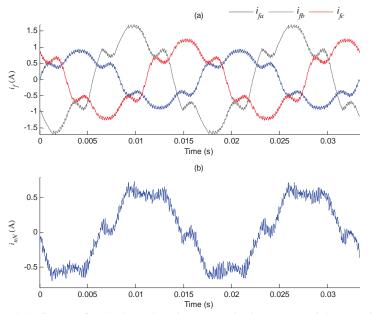

| Figure 2.19 Currents for the three-phase inverter (a) load currents, and (b) neutral current 29                         |

| Figure 2.20 Bifurcation diagram for the three-phase inverter: unbalanced case                                           |

| Figure 2.21 Three-phase Six-pulse converter    30                                                                       |

| Figure 2.22 Equivalent circuit of phase A                                                                               |

| Figure 2.23 Equivalent three-phase six-pulse converter model    31                                                      |

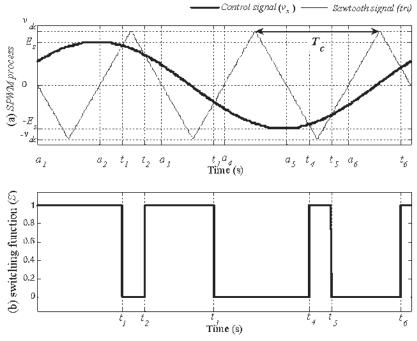

| Figure 2.24 Transforming a desired continuous signal v <sub>s</sub> into a SPWM signal                                  |

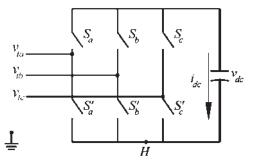

| Figure 2.25 Circuit of example 2.4                                                                                      |

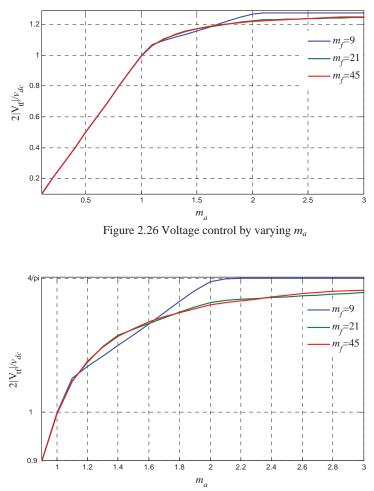

| <b>Figure 2.26</b> Voltage control by varying $m_a$                                                                     |

| Figure 2.27 Nonlinear range for magnitude of the fundamental frequency voltage control by                               |

| varying m <sub>a</sub>                                                                                                  |

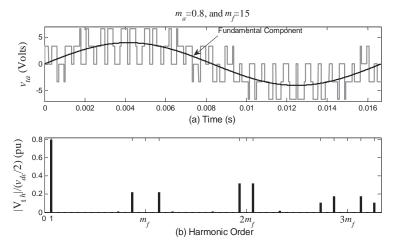

| Figure 2.28 Sinusoidal pulse width modulation (a) voltage at the terminal of the converter. (b)                         |

| Harmonic spectrum of the voltage at the terminal of the converter in terms of the dc voltage                            |

| capacitor                                                                                                               |

| Figure 2.29 Hysteresis modulation technique and the smooth hysteresis approximation                                     |

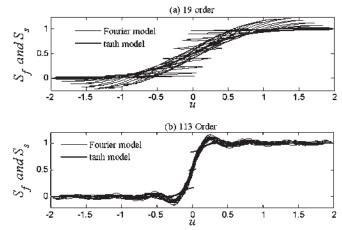

| Figure 3.1 Time domain comparison between the discontinuous switching function S and the                                |

| Fourier approach for different harmonic orders                                                                          |

| Figure 3.2 Spectrum comparison between the discontinuous switching function S and the Fourier                           |

| approach for different harmonic orders                                                                                  |

| Figure 3.3 Continuous switching function $S_s$ .46                                                                      |

| Figure 3.4 Continuous switching function and discrete switching function                                                |

| Figure 3.5 Commutation functions $S_f$ and $S_s$ for different harmonic orders and cutoff frequencies. 48               |

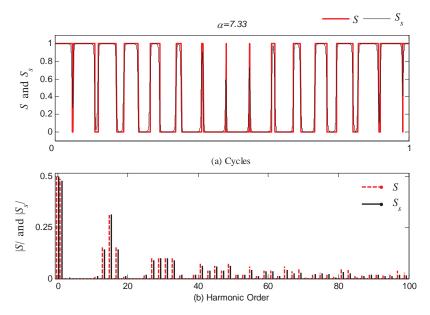

| Figure 3.6 Comparison between the discontinuous switching function S and the hyperbolic tangent                         |

| approach for $\alpha = 7.33$ . (a) Time domain waveforms, (b) Harmonic spectrum                                         |

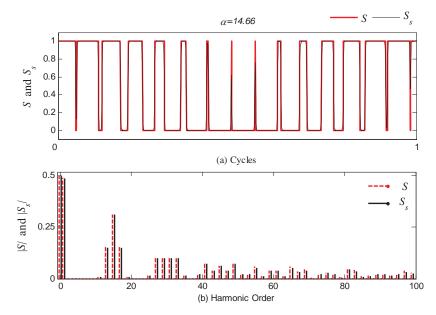

| Figure 3.7 Comparison between the discontinuous switching function S and the hyperbolic tangent                         |

| approach for $\alpha = 14.66$ . (a) Time domain waveforms, (b) Harmonic spectrum                                        |

| Figure 3.8 Single-phase test system.    50                                                                              |

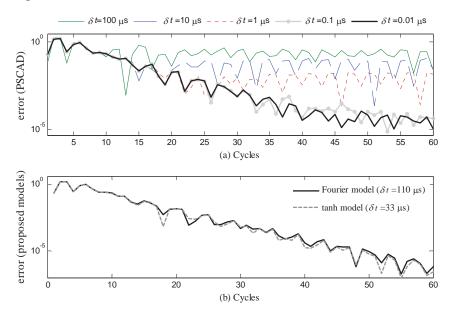

| Figure 3.9 Convergence error for the STATCOM. (a) PSCAD/EMTDC solution using the ideal                                  |

| switch model. (b) Solution obtained using the proposed models                                                           |

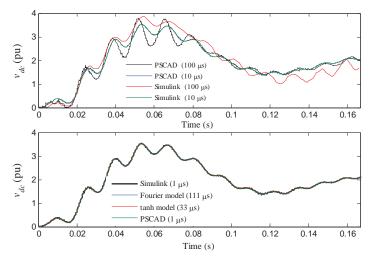

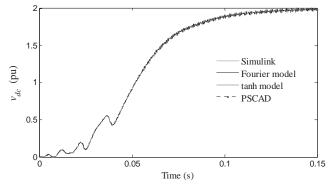

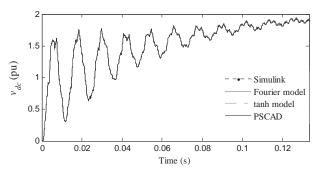

| Figure 3.10 Transient solution comparison for the STATCOM (a) Transient solution computed                               |

| using Simulink and PSCAD/EMTDC for the STATCOM. (b) Transient solution comparison for the                               |

| STATCOM between Simulink, PSCAD/EMTDC, and the proposed models                                                          |

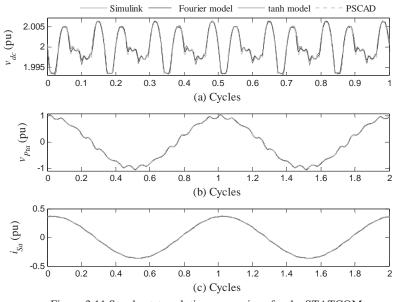

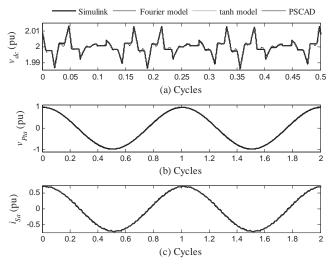

| Figure 3.11 Steady state solution comparison for the STATCOM.                                     | 52           |

|---------------------------------------------------------------------------------------------------|--------------|

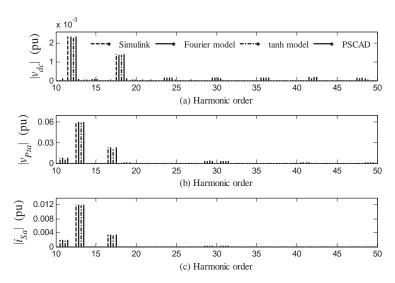

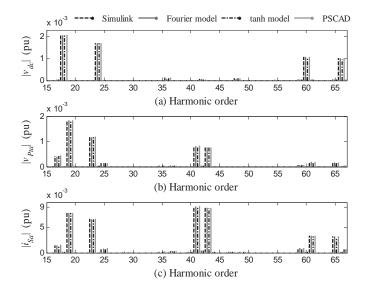

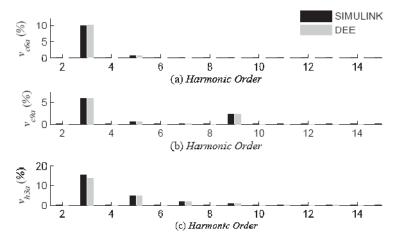

| Figure 3.12 Harmonic content comparisons. (a) Harmonic content in the dc voltage. (b)             | Magnitude    |

| of selected harmonics in phase A of the terminal voltage. (c) Magnitude of selected har           | rmonics in   |

| phase A of the series current                                                                     | 53           |

| Figure 3.13 SSSC control.                                                                         | 53           |

| Figure 3.14 Transient solution comparison for the SSSC.                                           | 54           |

| Figure 3.15 Steady state solution comparison for the SSSC.                                        | 54           |

| Figure 3.16 Harmonic content comparisons. (a) Harmonic content in the dc voltage. (b)             | Magnitude    |

| of selected harmonics in phase A of the terminal voltage. (c) Magnitude of selected har           | rmonics in   |

| the phase A of the series current                                                                 | 54           |

| Figure 3.17 Transient solution comparison for the UPFC.                                           | 55           |

| Figure 3.18 Steady-state solution comparison for the UPFC.                                        | 56           |

| Figure 3.19 Harmonic content comparisons. (a) Harmonic content in the dc voltage. (b)             | Magnitude    |

| of selected harmonics in phase A of the terminal voltage. (c) Magnitude of selected har           | rmonics in   |

| the phase A of the series current                                                                 | 56           |

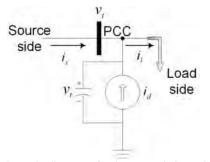

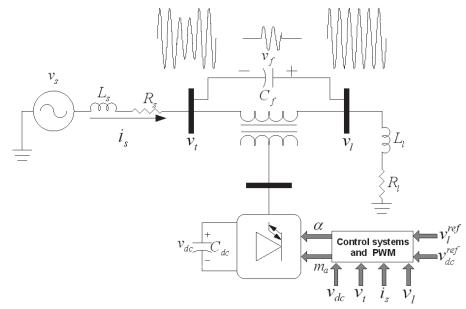

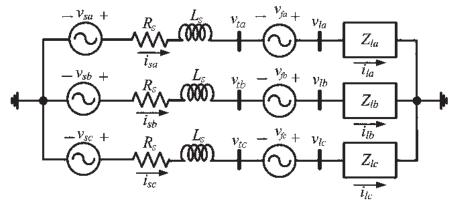

| Figure 3.20 Structure of the DSTATCOM.                                                            | 57           |

| Figure 3.21 Compensation of the EAF when the source is non-stiff and the DSTATCOM                 | contains a   |

| passive filter                                                                                    | 58           |

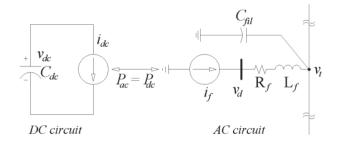

| Figure 3.22 Schematic representation for the simplified model                                     | 62           |

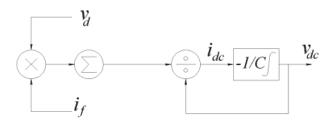

| Figure 3.23 dc link model                                                                         | 62           |

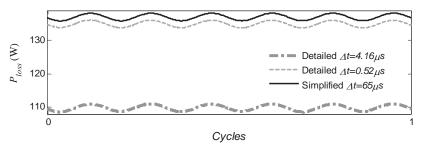

| Figure 3.24 Comparison in the time domain between the detailed and the simplified mode            | el for Ploss |

| in steady-state for different integration steps                                                   | 63           |

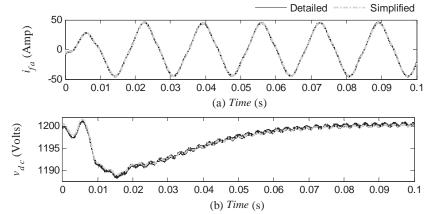

| Figure 3.25 Comparison in the time domain between the detailed and the simplified me              | odel for (a) |

| compensation current $i_{fa}$ and (b) dc capacitor voltage $v_{dc}$                               | 63           |

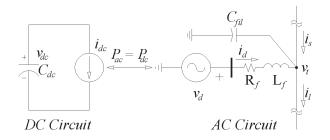

| Figure 3.26 Schematic representation for the simplified model                                     | 64           |

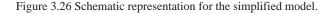

| Figure 3.27 dc link model                                                                         | 64           |

| Figure 3.28 Comparison in the time domain between the detailed and the simplified mo              | odel for (a) |

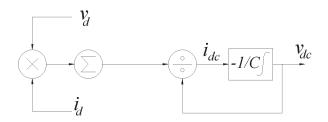

| phase angle $\delta$ , (b) dc capacitor voltage $v_{dc}$ , and (c) compensation current $i_{fa}$  | 67           |

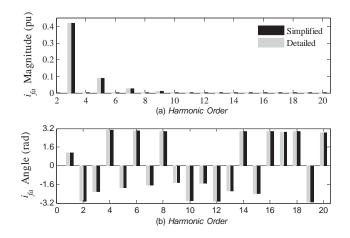

| <b>Figure 3.29</b> Spectrum comparison between the detailed and the simplified model for $i_{fa}$ | 67           |

| Figure 3.30 Comparison in the time domain between the detailed and the simplified mode            | el based on  |

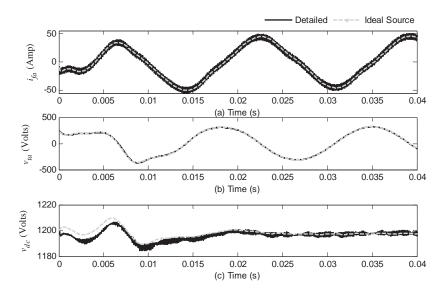

| the ideal source approach for (a) compensation current $i_{fa}$ , (b) terminal voltage $v_{ta}$ , | and (c) dc   |

| capacitor voltage v <sub>dc</sub> .                                                               | 68           |

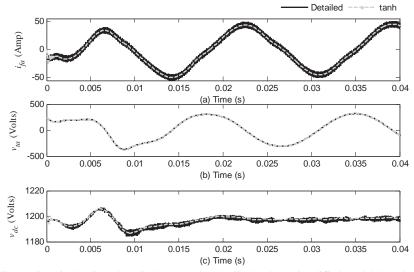

| Figure 3.31 Comparison in the time domain between the detailed and the simplified model base                                                                                                                                                                                                                      |  |                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------------------------|

| the ideal source approach for (a) compensation current $i_{fa}$ , (b) terminal voltage $v_{ta}$ , and                                                                                                                                                                                                             |  |                                                                                                |

| capacitor voltage v <sub>dc</sub> .                                                                                                                                                                                                                                                                               |  |                                                                                                |

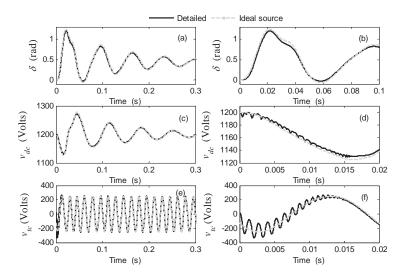

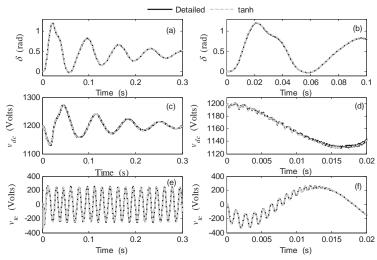

| <b>Figure 3.32</b> Comparison in the time domain between the detailed and the simplified based ideal source approach for (a) phase angle $\delta$ , (b) phase angle $\delta$ during the first 0.02 s capacitor voltage $v_{dc}$ , (d) dc capacitor voltage $v_{dc}$ during the first 0.02 s, (e) terminal voltage |  |                                                                                                |

|                                                                                                                                                                                                                                                                                                                   |  | (f) terminal voltage $v_{tc}$ during the first 0.02 s                                          |

|                                                                                                                                                                                                                                                                                                                   |  | Figure 3.33 Comparison in the time domain between the detailed and the simplified based on the |

| sigmoid function approach for (a) phase angle $\delta$ , (b) phase angle $\delta$ during the first 0.02 s,(c) de                                                                                                                                                                                                  |  |                                                                                                |

| capacitor voltage $v_{dc}$ , (d) dc capacitor voltage $v_{dc}$ during the first 0.02 s, (e) terminal voltage $v_{tc}$ ,                                                                                                                                                                                           |  |                                                                                                |

| (f) terminal voltage $v_{tc}$ during the first 0.02 s                                                                                                                                                                                                                                                             |  |                                                                                                |

| Figure 3.34 DVR inserting voltage to protect a sensitive load                                                                                                                                                                                                                                                     |  |                                                                                                |

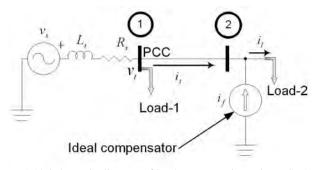

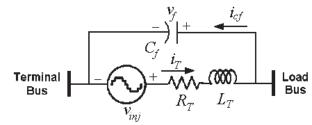

| Figure 3.35 Schematic diagram of a distribution system with ideal series compensator                                                                                                                                                                                                                              |  |                                                                                                |

| Figure 3.36 Single-phase equivalent circuit of the DVR with filter capacitor connected in shunt                                                                                                                                                                                                                   |  |                                                                                                |

| with the DVR                                                                                                                                                                                                                                                                                                      |  |                                                                                                |

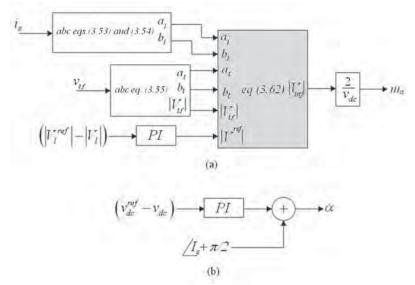

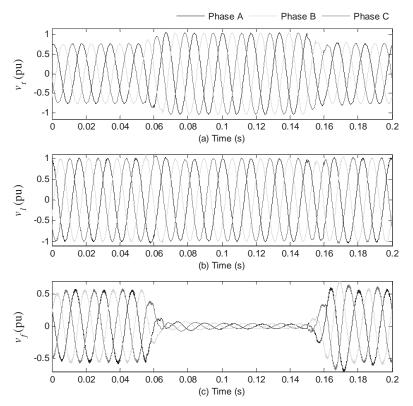

| Figure 3.37 Circuit control of the DVR.    73                                                                                                                                                                                                                                                                     |  |                                                                                                |

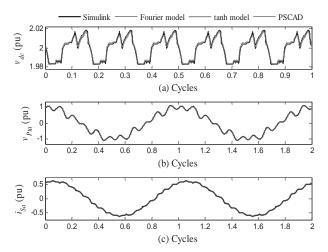

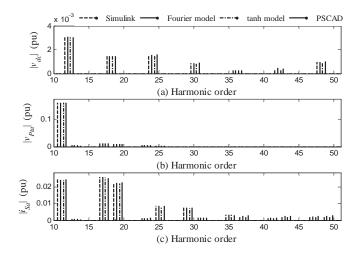

| Figure 3.38 Transient solutions for the operation of the DVR. (a) Terminal voltage, (b) Load                                                                                                                                                                                                                      |  |                                                                                                |

| voltage, and (c) Compensation voltage                                                                                                                                                                                                                                                                             |  |                                                                                                |

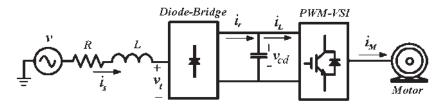

| Figure 3.39 Experimental system configuration.    76                                                                                                                                                                                                                                                              |  |                                                                                                |

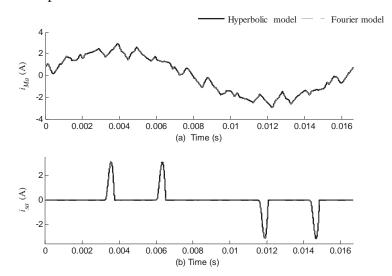

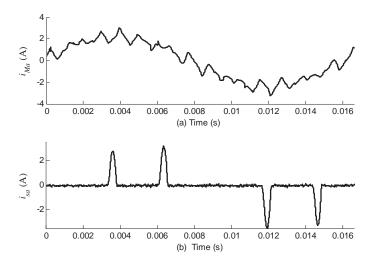

| Figure 3.40 Simulated waveforms (a) Motor current of phase A (b) Rectifier current of phase A77                                                                                                                                                                                                                   |  |                                                                                                |

| Figure 3.41 Experimental waveforms (a) Motor current of phase A (b) Rectifier current of phase A.                                                                                                                                                                                                                 |  |                                                                                                |

|                                                                                                                                                                                                                                                                                                                   |  |                                                                                                |

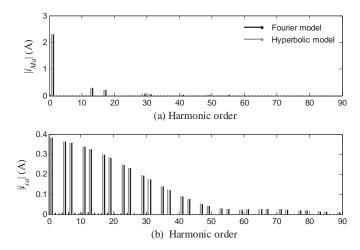

| Figure 3.42 Harmonic content computed with proposed models. (a) Harmonic content in the motor                                                                                                                                                                                                                     |  |                                                                                                |

| current of phase A. (b) content in the rectifier current of phase A                                                                                                                                                                                                                                               |  |                                                                                                |

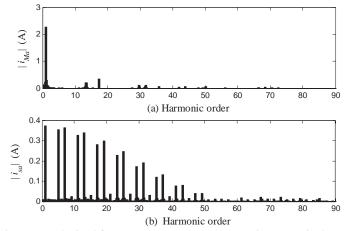

| Figure 3.43 Harmonic content obtained from measurements. (a) Harmonic content in the motor                                                                                                                                                                                                                        |  |                                                                                                |

| current of phase A. (b) content in the rectifier current of phase A                                                                                                                                                                                                                                               |  |                                                                                                |

| Figure 4.1 Schematic representation of the test system with the six-pulse rectifier                                                                                                                                                                                                                               |  |                                                                                                |

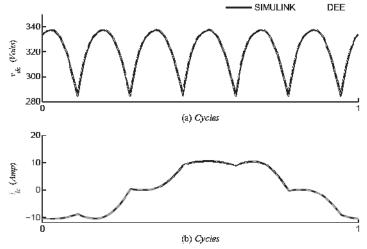

| <b>Figure 4.2</b> Selected waveforms. (a) dc voltage $v_{dc}$ (b) ac current $i_{lc}$                                                                                                                                                                                                                             |  |                                                                                                |

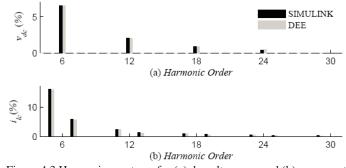

| <b>Figure 4.3</b> <i>Harmonic spectrum for</i> ( <i>a</i> ) <i>dc voltage</i> $v_{dc}$ <i>, and</i> ( <i>b</i> ) <i>ac current</i> $i_{lc}$                                                                                                                                                                       |  |                                                                                                |

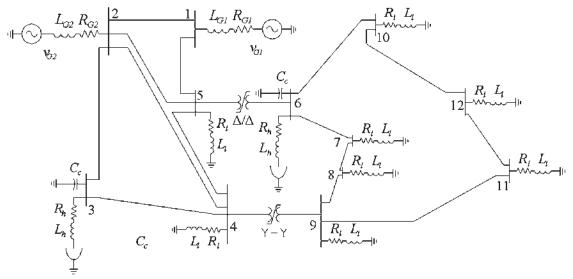

| Figure 4.4 Twelve-node three phase test system       88                                                                                                                                                                                                                                                           |  |                                                                                                |

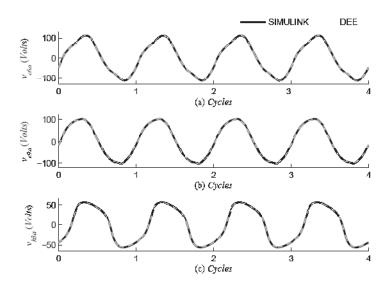

| <b>Figure 4.5</b> Selected waveforms for the twelve-node three phase test system. (a) $v_{c6a}$ (b) $v_{c9a}$ and (c)                                                                                                                                                                                             |  |                                                                                                |

| <i>v</i> <sub>h3a</sub>                                                                                                                                                                                                                                                                                           |  |                                                                                                |

| <b>Figure 4.6</b> Harmonic spectrum for the twelve-node three phase test system. (a) $v_{c6a}$ (b) $v_{c9a}$ and (c)                                                                                                                                                                                              |  |                                                                                                |

| <i>v</i> <sub>h3a</sub>                                                                                                                                                                                                                                                                                           |  |                                                                                                |

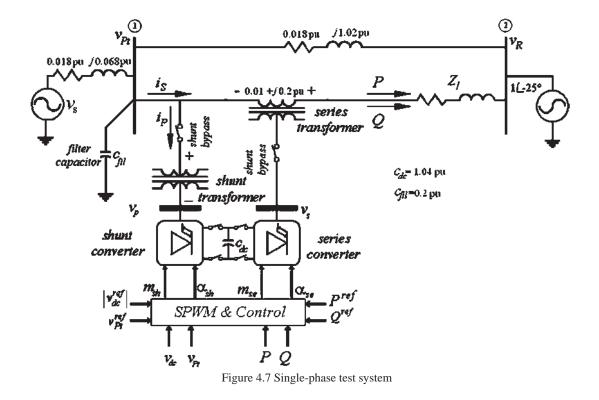

| Figure 4.7 Single-phase test system                                                                                                              |                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

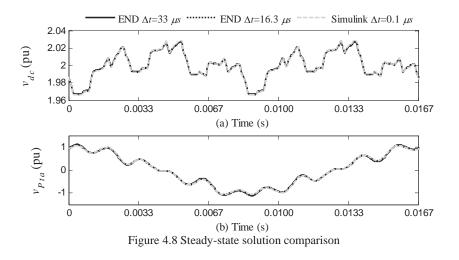

| Figure 4.8 Steady-state solution comparison                                                                                                      |                         |

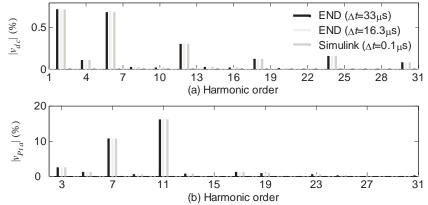

| Figure 4.9 Harmonic content comparisons. (a) Harmonic content in the dc voltage. (b)                                                             | Harmonics               |

| in phase A of the terminal voltage. (c) Harmonics in the phase A of the series current                                                           |                         |

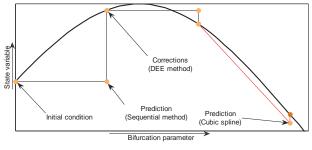

| Figure 5.1 Continuation method                                                                                                                   |                         |

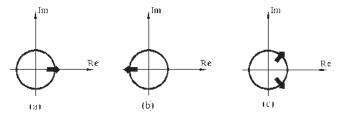

| Figure 5.2 Three scenarios for the loss of stability of a solution: (a) Fold bifurcation.                                                        | (b) Period              |

| double bifurcation. (c) Neimark-Sacker bifurcation.                                                                                              |                         |

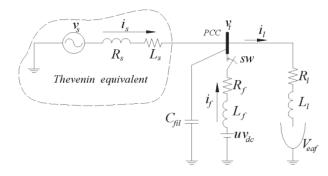

| Figure 5.3 Compensation of the EAF when the source is non-stiff and the DSTATCOM                                                                 | contains a              |

| passive filter                                                                                                                                   | 100                     |

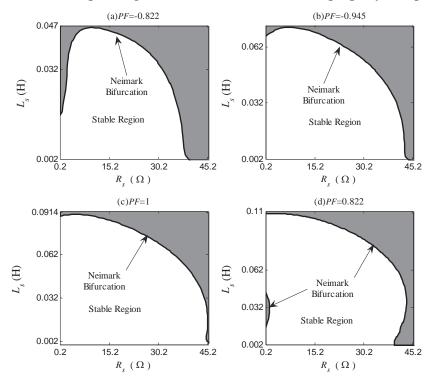

| Figure 5.4 Stability regions for the DSTATCOM operating in current control for diffe                                                             | rent power              |

| factors at the terminal bus with $ V_s $ =440 Volts                                                                                              | 101                     |

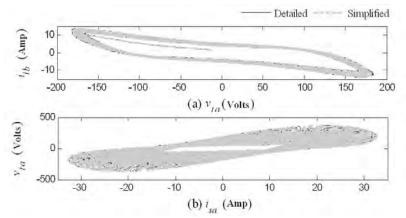

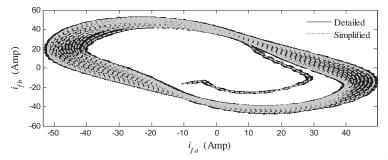

| <b>Figure 5.5</b> <i>Phase portrait for different operating points.</i> (a) <i>Phase portrait in the</i> $v_{ta} - i_{lb}$                       | plane with              |

| $PF=1$ , $L_s=87.77$ mH, and $R_s=12.1 \Omega$ . (b) Phase portrait in the $i_{sa} - v_{ta}$ plane with $PF=0$ .                                 | 822, L <sub>s</sub> =30 |

| mH, and $R_s=1 \ \Omega$                                                                                                                         | 102                     |

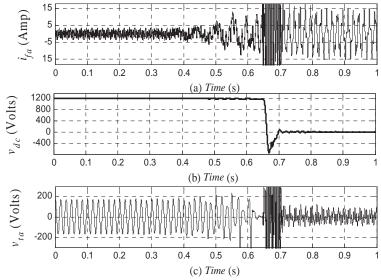

| <b>Figure 5.6</b> Simulated waveforms for $PF=0$ , $L_s=87.77$ mH, and $R_s=25 \Omega$ . (a) Compensation                                        | tor current             |

| $i_{fav}$ . (b) dc capacitor voltage $v_{dc}$ . (c) Terminal voltage $v_{ta}$                                                                    | 102                     |

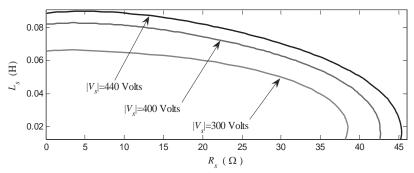

| Figure 5.7 Stability regions for the DSTATCOM operating in current control for $ V_s $ =                                                         | =440 Volts,             |

| for $ V_s $ =400 Volts, and for $ V_s $ =300 Volts with PF=1                                                                                     | 103                     |

| Figure 5.8 Stability regions for the DSTATCOM operating in current control mode                                                                  | in (a) the              |

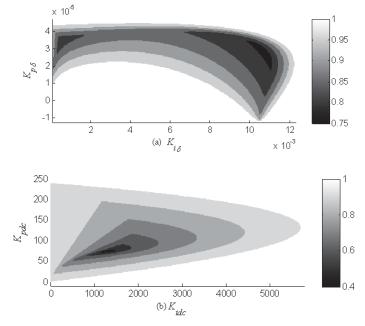

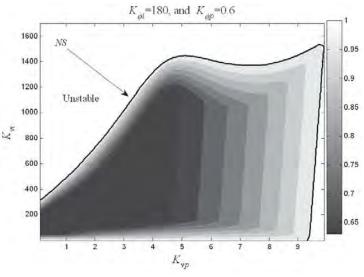

| $K_{idc}$ - $K_{pdc}$ space, and (b) $K_{i\beta}$ - $K_{p\beta}$ space                                                                           | 104                     |

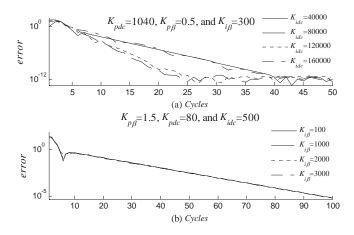

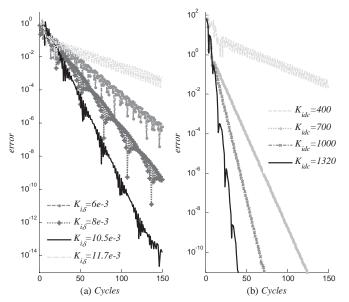

| Figure 5.9 Convergence error for different gains in the DSTATCOM controllers.                                                                    | (a) For dc              |

| capacitor voltage controller. (b) For power factor controller                                                                                    | 104                     |

| <b>Figure 5.10</b> <i>Quasiperiodic solution for</i> $K_{p\beta}$ =0.5, $K_{i\beta}$ =300, $K_{pdc}$ =1040, and $K_{idc}$ =2.5×10 <sup>5</sup> . | $i_{fa} v_s i_{fb} 105$ |

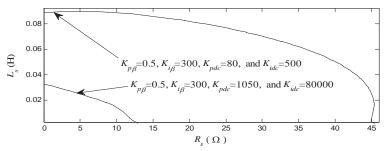

| Figure 5.11 Comparison between the stability regions for two different set of gains                                                              | 105                     |

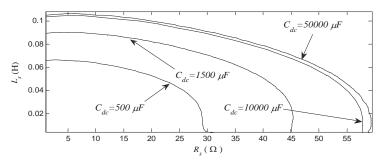

| Figure 5.12 Comparison between the stability regions for different dc capacitors                                                                 | 105                     |

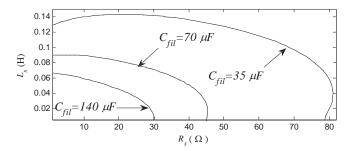

| Figure 5.13 Comparison between the stability regions for different ac capacitors                                                                 | 106                     |

| Figure 5.14 Stability regions for the DSTATCOM operating in voltage control in the $L_s$                                                         | - R <sub>s</sub> plane  |

| for different Thevenin equivalent voltages; (a) $ V_m =350$ Volts, (b) $ V_m =400$ Volt                                                          | s, and (c)              |

| /V <sub>m</sub> /=440 Volts. (d) Comparison of the stability boundaries                                                                          | 108                     |

| <b>Figure 5.15</b> <i>Time domain solutions.</i> (a) $v_{dc}$ , (b) $v_{ta}$ , and (c) $i_{sa}$ for $R_s=1 \ \Omega$ , $L_s=0.2 \ mH$ , and      | $d  V_m  = 440$         |

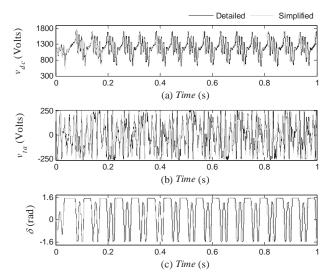

| Volts.                                                                                                                                           | 109                     |

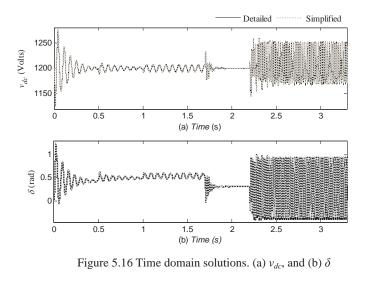

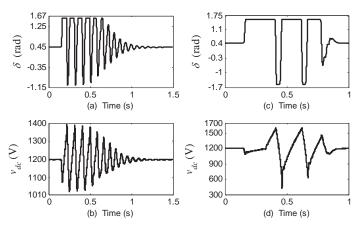

| <b>Figure 5.16</b> <i>Time domain solutions.</i> ( <i>a</i> ) $v_{dc}$ , and ( <i>b</i> ) $\delta$                                               | 110                     |

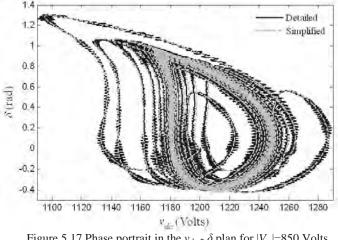

| <b>Figure 5.17</b> <i>Phase portrait in the</i> $v_{dc}$ - $\delta$ <i>plan for</i> $ V_m $ = 850 <i>Volts</i>                                   | 110                     |

| Figure A.2 STATCOM control configuration | 132 |

|------------------------------------------|-----|

| Figure A.3 SSSC control scheme           | 134 |

# **List of Tables**

| Table 1.1 | Overview of the principal FACTS-Devices                         | 1          |

|-----------|-----------------------------------------------------------------|------------|

| Table 3.1 | System Parameters of The DSTATCOM in Current Mode               | 52         |

| Table 3.2 | System Parameters of The DSTATCOM in Voltage Mode               | 56         |

| Table 3.3 | System Parameters of The DVR                                    | 74         |

| Table 3.4 | Induction Motor Parameters                                      | 76         |

| Table 3.5 | System Parameters                                               | 77         |

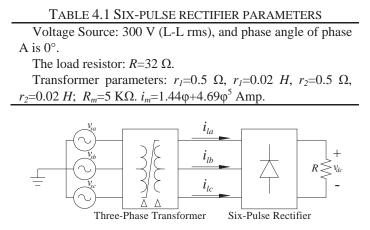

| Table 4.1 | Six-pulse rectifier parameters 8                                | 36         |

| Table 4.2 | Mismatches During Convergence of The ND,FD and DEE Methods      | 37         |

| Table 4.3 | Twelve-node parameters                                          | 38         |

| Table 4.4 | Mismatches During Convergence of The ND, AT, FD and DEE Methods | 39         |

| Table 4.5 | Mismatches During Convergence of The DEE Method                 | <i>)</i> 0 |

| Table 4.6 | Mismatches During Convergence of The BF, ND and END Methods     | <b>)</b> 5 |

# **List of Publications**

The following publications are associated with this research work:

#### Indexed papers by Journal Citation Reports (JCR):

- Segundo-Ramírez, J., and Medina, A. "Periodic Steady-State Solution of Electric Systems Including UPFCs by Extrapolation to the Limit Cycle." IEEE Transaction on Power Delivery, vol. 23, no. 3 (July 2008): 1506 - 1512. Impact Factor: 1.289.

- Segundo-Ramírez, J., Medina, A., Ghosh, A. and Ledwich, G. "Stability Analysis Based on Bifurcation Theory of the DSTATCOM Operating in Current Control Mode." IEEE Transaction on Power Delivery, vol. 24, no. 3 (July 2009): 1670-1678. Impact Factor: 1.289.

- 3) Segundo-Ramírez, J., and Medina, A. "Modeling of FACTS Devices Based on SPWM VSCs." IEEE Transaction on Power Delivery, vol. 24, no. 4 (October 2009): 1815-1823. Impact Factor: 1.289.

- 4) Segundo-Ramírez, J., and Medina, A. "Computation of the Steady-State Solution of Nonlinear Power Systems by Extrapolation to the Limit Cycle Using a Discrete Exponential Expansion Method." International Journal of Nonlinear Sciences and Numerical Simulation, 2009. (Accepted). Impact Factor: 8.479.

- 5) Segundo-Ramírez, J., and Medina, A. "An Enhanced Process for the Fast Periodic Steady State Solution of Nonlinear Systems by Poincaré Map and Extrapolation to the Limit Cycle." International Journal of Nonlinear Sciences and Numerical Simulation, 2009. (Accepted). Impact Factor: 8.479.

- 6) Segundo-Ramírez, J., Medina, A., Ghosh, A. and Ledwich, G. "Nonlinear Oscillations Assessment of the DSTATCOM Operating in Voltage Control Mode." Electric Power Components and Systems," (Accepted). Impact Factor: 0.376.

- Ramos-Carranza, A. Medina, A. Segundo-Ramírez, J. and Madrigal, M. "Shunt Hybrid Filter Control for Harmonic Current Mitigation and Reactive Power Compensation in Electric Systems." Transaction on Power Delivery (Under review). Impact Factor: 1.289.

- Segundo-Ramírez, J., Medina, A., Ghosh, A. and Ledwich, G. "Stability Analysis Based on Bifurcation Theory and Continuation Techniques of a Capacitor-Supported DVR Including Harmonic Distortion." Transaction on Power Delivery (Under review). Impact Factor: 1.289.

Segundo-Ramírez, J., Bárcenas, E., Medina, A., and Cárdenas, V. "Steady-State and Dynamic State-Space Model for Efficient Solution and Stability Assessment of ASDs." (To be submitted)

#### **Conference Papers:**

- 1) Segundo-Ramírez, J., and Medina, A. "Periodic Steady State Solution of Electric Systems Including UPFCs." *PES General Meeting*, July 2008: 1-1.

- 2) Segundo-Ramírez, J., and A. Medina. "Transient and Steady-State Analysis of the UPFC Using a Fourier Series Approach Model." 13th International Conference on Harmonics and Power Quality. Wollongong, 2008. 1-6.

- 3) Segundo-Ramírez, J., and A. Medina. "Periodic Steady State Solution of FACTS Devices Based on SPWM VSCs." IEEE ISIE 2009, 5-8 July 2009: 1644-1649.

# Abstract

This thesis presents the modeling of electric power systems including FACTS and Custom Power (CP) devices and their stability analysis through application of bifurcation theory, continuation methods, and Newton methods to compute the periodic steady state.

The previous stability analyses of FACTS and Custom Power devices based on bifurcation theory using continuation methods neglected the harmonic distortion introduced by the voltage source converter (VSC). Besides, the network transients have not been taken into account. Under this formulation, the electric power network was modeled through a phasor representation, and obviously, only the fundamental frequency was considered in those analyses.

In this research, two VSC models based on Fourier series and hyperbolic tangent function are proposed. The proposed models can be used for fast simulation in the time domain of power-electronic devices based on sinusoidal pulse-width modulation VSCs; the undesirable error introduced by the high commutates rates are removed; even though the harmonic distortion coming from the converter is taken into account. The switching instants in the Fourier model are approximated in a closed form, and an iterative algorithm based on the Newton-Raphson method is developed for the exact calculation of the switching instants. The hyperbolic tangent model does not need the calculation of the switching instants as in the case of the Fourier model. With these VSC's models the computation of the periodic steady-state solution of power systems including FACTS is efficiently obtained by extrapolation to the limit cycle using a Newton method. In addition, it is possible to assess the stability through the Floquet multiplier. Two Newton methods to compute efficiently the periodic steady state solution are presented. One is based on an Enhanced Numerical Differentiation technique, and the other one is based on Discrete Exponential Expansion approach of the transition matrix. These methods prove to be more efficient than the conventional methods such as [Aprille Jr. and Trick 1972], [Colon and Trick 1973], and [Semlyen and Medina 1995]. It is also presented the stability analysis for a distribution static compensator (DSTATCOM) that operates in current control mode and voltage control mode based on bifurcation theory. A control design for the DSTATCOM is proposed. Along with this control, a suitable mathematical representation of the DSTATCOM is proposed. In addition, the stability analysis for a capacitor-supported dynamic voltage restorer (DVR) based on bifurcation theory and a continuation method is presented. The stability regions in the Thevenin equivalent plane are computed for different operating scenarios. In addition, the stability regions in the control gain space, as well as the contour lines for different Floquet multipliers are computed.

The proposed models and analysis are validated against the solution obtained with the power system blockset of Simulink and with PSCAD/EMTDC. Additionally, the proposed VSC models based on the Fourier series and the hyperbolic tangent approach are validated against the response obtained by measurements from a 1.5 kVA ASD experimental setup system.

# Acknowledgment

I would like to express my best acknowledgments and gratefulness to my family, especially to my beautiful wife.

Thanks to my friends at Universidad Michoacana de San Nicolás de Hidalgo (UMSNH) and Queensland University of Technology (QUT) for their helpful advice and discussions throughout the course of my work.

I would like to express my thanks and gratitude to my supervisor Dr. Aurelio Medina-Rios, for his invaluable technical support, incessant encouragement, friendship and understanding. During these years of working together has given me faith and confidence to become an independent researcher for which I am thankful.

Thanks a lot to Professors A. Ghosh and G. Ledwich and all the professors for their generosity in the review of this thesis.

I gratefully acknowledge the financial assistance given by the Consejo Nacional de Ciencia y Tecnología (CONACYT), México during my PhD studies.

Flexible ac Transmission Systems (FACTS), provide higher controllability in power systems by means of power electronic devices. Several FACTS devices have been already introduced for various applications worldwide. A number of new types of devices are in the stage of being introduced in practice. Even more concepts of configurations of FACTS-devices are discussed in research and literature. FACTS technology provides a better ability to varying operational conditions and improve the usage of existing installations.

## **1.1 State of the Art**

It can be seen that with growing line length and with higher power demand the opportunity for FACTS devices gets more important. The devices work electrically as fast current, voltage or impedance controllers. The power electronic allows very short reaction times down to far below one second (~ms). Detailed introductions in FACTS devices can also be found in the literature [Hingorani and Gyudyi 2000] [Sood 2004] [Acha, et al. 2004] [Mathur and Varma 2002] [Padiyar 2007] [Zhang, et al. 2006] with the main focus on basic technology, modeling and control.

Basically, there are two groups of FACTS, one is based on thyristor valve operation [Hingorani and Gyudyi 2000], and the other is based on Voltage Source Converters (VSCs) [Segundo-Ramírez and Medina 2008] [Segundo-Ramírez and Medina 2009]. A list of some FACTS devices are shown in Table 1.1.

| Connection Type            | FACTS Devices                                     |                                                 |  |

|----------------------------|---------------------------------------------------|-------------------------------------------------|--|

|                            | Thyristor-Based FACTS                             | VSC-Based FACTS                                 |  |

| Shunt Connected            | Static Var Compensator (SVC)                      | Static Compensator (STATCOM)                    |  |

| Series Connected           | Thyristor Controlled Series<br>Compensator (TCSC) | Static Series Synchronous<br>Compensator (SSSC) |  |

| Shunt and Series Connected | HVDC                                              | Unified Power Flow Controller<br>(UPFC)         |  |

|                            |                                                   | HVDC VSC                                        |  |

TABLE 1.1 OVERVIEW OF THE PRINCIPAL FACTS-DEVICES

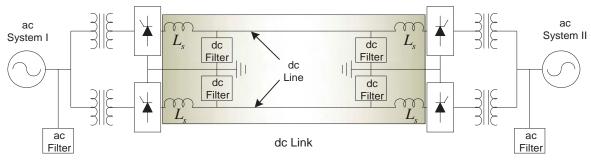

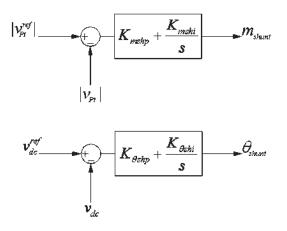

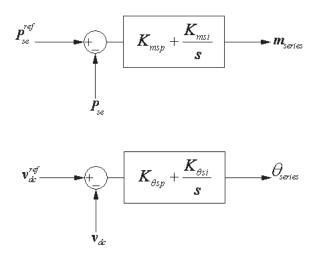

The FACTS devices based on VSCs provide a controllable voltage magnitude and phase angle due to a Pulse Width Modulation (PWM) technique [Mohan, et al. 1995]. The Static Compensator (STATCOM) [Hingorani and Gyudyi 2000] is a shunt connected device that is able to provide reactive power support at a network location far away from the generators. Through this reactive power injection, the STATCOM can regulate the voltage at the connection node. The Static Synchronous Series compensator (SSSC) [Hingorani and Gyudyi 2000] is a series device which injects a voltage in series with the transmission line. The Unified Power Flow Controller (UPFC) [Hingorani and Gyudyi 2000] is the most versatile device of the family of FACTS devices, since it is able to control the active and the reactive power, respectively, as well as the voltage at the connection node. In Figure 1.1 a schematic representation of the STATCOM, the SSSC, and the UPFC are presented. The mathematical representation adopted in this thesis is the state space approach of nonautonomous nonlinear ODE sets periodically forced, where the electric transients and the harmonic distortion are not neglected. Additionally, all the state variables are in instantaneous values, thus the steady-state solution is a limit cycle. In the conventional stability analysis of power systems including FACTS and CP devices [Srivastava and Srivastava 1998], the power system is represented using Root Mean Square (RMS) quantities, and the network transients are neglected

Figure 1.1 FACTS devices based on VSCs. (a) STATCOM, (b) SSSC, and (c) UPFC

To explore both stable and unstable limit cycles [Parker and Chua 1989], the bifurcation analysis is used; a nonlinear mathematical theory [Parker and Chua 1989] [Nayfeh and Balachandran 1995] used to qualitatively investigate how the integral curves change as the parameters are varied. The bifurcation theory has been applied to the analysis of voltage collapse [Dobson and Chiang 1989], analysis of the Electric Arc Furnace (EAF) [Medina, et al. 2005], chaotic oscillations [Wang, et al. 1994], ferroresonance analysis [Wörnle, et al. 2005], and the design of nonlinear controllers [Lee, et al. 2001]. It has also been applied to assess the dynamic behaviour of nonlinear components such as induction motors [Rosehart and Cañizares 1999], load models [Cañizares 1995] [Pai, et al. 1995], tap changing transformers [Vu and Liu 1989], and FACTS devices [Srivastava and Srivastava 1998] [Mithulananthan, et al. 2003].

In power electronic, the bifurcation theory has been used successfully to analyze the stability of power converters and switched circuits [Azzouz, et al. 1983] [Zhusubaliyev and

Mosekilde 2006] [Jalali, et al. 1996] [di Bernardo and Vasca 2000] [di Bernardo, et al. 1998] [lu and Robert 2003] [Tse 2004] [Deane and Hamill 1990]. Conventionally, this analysis is carried-out with the discrete-time iterative mapping approach [Zhusubaliyev and Mosekilde 2006] [Jalali, et al. 1996] [di Bernardo and Vasca 2000] [di Bernardo, Garofalo, et al. 1998] [lu and Robert 2003] [Tse 2004]. Under this approach, the switching converter is essentially modeled as piecewise switched circuits. This results in a nonlinear time-varying operating mode, which naturally demands the use of nonlinear theory [Tse 2004]. In the discrete-time iterative mapping approach, it is assumed that between switching instants, the network is linear time-invariant. Thus, the solution between switches can be found in a closed-form. Here, the nonlinearity comes from the switching control.

The previous stability analyses of FACTS and Custom Power devices based on bifurcation theory using continuation methods neglected the harmonic distortion introduced by the voltage source converter (VSC). Besides, the network transients have not been taken into account. Under this formulation, the electric power network was modeled through a phasor representation, and obviously, only the fundamental frequency was considered in those analyses.

The compensating FACTS devices based on VSCs, under analysis in this investigation are briefly described below.

#### **1.1.1 Static Compensator (STATCOM)**

It is a shunt device that does not require passive elements for reactive compensation. The STATCOM operation is based on a VSC, which is supplied by a dc storage capacitor. The VSC terminals are connected to the dc system through a coupling transformer. The VSC produces a quasi-sine wave voltage at the fundamental frequency (50 or 60 Hz). The STATCOM can generate or absorb reactive power. A schematic representation of the STATCOM is shown in Figure 1.1(a).

Assuming that the losses in the VSC and the coupling transformer are negligible,  $v_{statcom}$  is in phase with the voltage at the terminal bus  $v_k$ . In this situation, the current  $i_{statcom}$  is completely reactive. If the magnitude of the voltage  $v_k$  is more than the magnitude of  $v_{statcom}$ , the reactive current flows from the bus to the VSC, which means that the STACOM absorbs reactive power. On the other hand, if the magnitude of  $v_{statcom}$  is more than the magnitude of  $v_k$ , the reactive current flows from the VSC to the ac system. Then, the STATCOM injects reactive power to the system. In practice, the power losses of the STATCOM are not negligible and must be drawn from the ac system to maintain constant the dc capacitor voltage.

#### **1.1.2 Static Synchronous Series Compensator (SSSC)**

The SSSC is a series device in which a synchronous voltage source injects a fundamental frequency voltage in series with the transmission line through a coupling transformer. The synchronous voltage source is supplied by a VSC. A schematic representation of the SSSC is shown in Figure 1.1(b)

Ideally, the injected voltage is in quadrature with the line current. In this mode the VSC does not absorb or generate any real power. However, in practice, the VSC losses must be

replenished by the ac system, in consequence a small phase lag is introduced for this purpose. There are two modes of operation of this device, one is in which the injected voltage is proportional to the line current and the other in which the injected voltage is independent of the line current [Gyugyi, et al. 1997]. The operating characteristics make this device very attractive for power transmission application. The main limitation of application is due to the losses and cost of the converter. The SSSC is a device which has so far not been built at transmission level because Series Compensator (fixed capacitor) and TCSC [Hingorani and Gyudyi 2000] are fulfilling all the today's operational requirements and a lower cost.

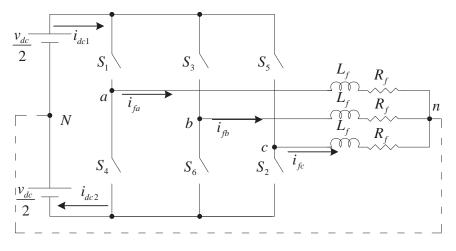

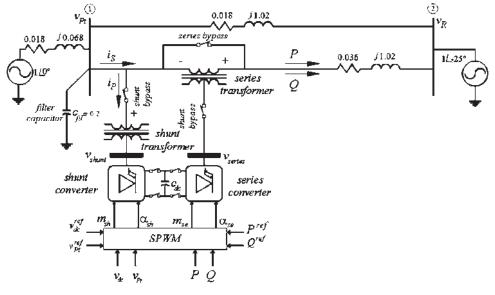

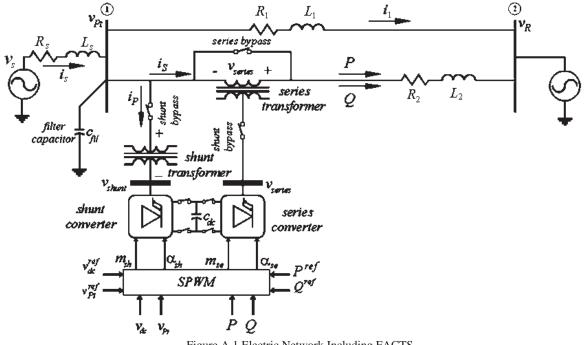

#### **1.1.3 Unified Power Flow Controller (UPFC)**

This device contains two VSCs connected together through a dc link storage capacitor. One of the VSCs is connected in series with the transmission line, while the other VSC is connected in shunt with the transmission line. The UPFC can control the active and reactive power flow in the transmission line, and at the same time can regulate the voltage magnitude at the connection node. To control the real and reactive power flow in the series side, the UPFC allows interchange of real power between the shunt and the series converters. The main disadvantage of this device is the high cost level due to the complex systems setup [Zhang, et al. 2006]. A schematic representation of the UPFC is shown in Figure 1.1(c).

#### **1.1.4 Other FACTS Devices**

#### 1.1.4.1 Static Var Compensator (SVC)

The Static Var Compensators are mainly used in power systems for voltage control. Some other application can be achieved, for example, for stabilization of power oscillations, or for improving transient stability [Hingorani and Gyudyi 2000] [Zhang, et al. 2006].

The SVC behaves like a shunt-connected variable reactance, which generates or absorbs reactive power in order to regulate the voltage magnitude at the point of connection to the ac network. The thyristor's firing angle control enables the SVC to swiftly respond

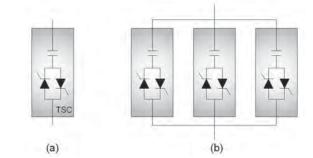

There are two main building blocks for SVCs; Thyristor Switched Capacitor (TSC) and Thyristor Controlled Reactor (TCR). The TSC is shown in Figure 1.2(a). In this configuration, a capacitor is connected in series with two opposite poled thyristors. Current flows through the device can be stopped by blocking the thyristors, and as a consequence the TCS behaves like a variable capacitive reactance. In practical applications, the TCS always comes in a group as shown in Figure 1.2(b).

A TCR is a reactor connected in series with two opposite poled thyristors. A schematic diagram of a TCR is shown in Figure 1.3. The firing signal for each thyristor is delayed by an angle  $\alpha$  from the zero crossing of the  $v_s$ . This angle, often called conduction angle, is shown in Figure 1.4. This Figure shows the typical TCR steady state voltage-current waveform. Conduction angle must be between 90° and 180°. Observe that for  $\alpha = 90^\circ$ , the

current waveform will be continuous and purely sinusoidal, and for  $\alpha = 180^{\circ}$ , the current will be zero.

Figure 1.2 (a) Schematic diagram of a TSC, and (b) multiple TSC connection

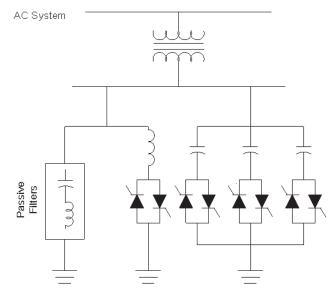

A practical SVC frequently contains both TCS modules and TCR, as shown in Figure 1.5. In addition, the SVC would contain a Fixed Capacitor (FC). The tuned filters are included to suppress harmonic current flowing into the ac system. The SVC contains firing and control circuits. The SVC is connected in shunt to an ac line through a step down transformer. The SVC is placed in the middle of the transmission line for line power and voltage regulation [Gyudyi 1988]. The SVCs can be placed close to loads to provide voltage support at the load bus, thereby avoiding possible voltage instability.

Figure 1.4 Steady state voltage-current waveform of a TCR

Figure 1.5 SVC connected to an ac network

#### 1.1.4.2 Thyristor Controlled Series Compensator (TCSC)

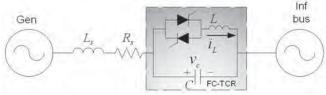

The Thyristor Controller Series Capacitor [Kinney, et al. 1995] [Hingorani and Gyudyi 2000] contains an ac Fixed Capacitor (FC) that is connected in parallel with a TCR. A schematic representation of the TCSC is shown in Figure 1.6.

Figure 1.6 Schematic Representation of a TCSC

Since this is a series compensation device, its placement is not that crucial and it can be placed anywhere along the line. The equivalent reactance of the parallel combination of a TCR with a fundamental reactance of  $X_L(\alpha)$  and a capacitance with a reactance of  $X_C$  is given by,

$$X_{eq}(\alpha) = \frac{X_C X_L(\alpha)}{X_C - X_L(\alpha)}$$

(1.1)

It can be noticed from (1.1) that by varying  $X_L(\alpha)$  the equivalent reactance can be inductive or capacitive. The gating signal of each thyristor is delayed by a firing angle  $\alpha$ , from the zero crossing of  $v_c$ . There are many ways of computing the fundamental frequency reactance of  $X_L(\alpha)$  [Christl, et al. 1992] [Fuerte-Esquivel, et al. 2000]. The voltage-current characteristic of the TCSC is very similar to that shown in Figure 1.4.

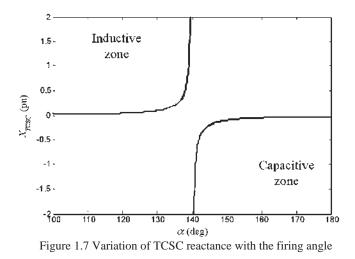

The variation of per-unit TCSC reactance,  $X_{eq}$ , as a function of the firing angle  $\alpha$ , is shown in Figure 1.7.

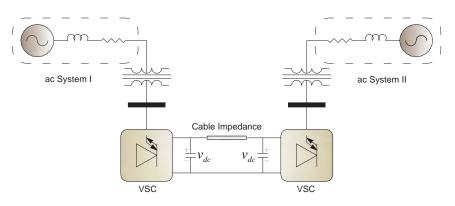

#### 1.1.4.3 High Voltage Direct Current (HVDC) Transmission

The application of power electronics in power systems started with bulk power transmission through High Voltage Direct Current. The schematic diagram of a double-poled HVDC transmission system linking two ac systems is shown in Figure 1.8. One of these converters is for the positive pole, and the other for the negative pole. The converters are thyristors built and are supplied from the three-phase ac side through transformers. In addition, at the point of coupling of the ac system and the dc system, tuned ac filters are connected so that harmonics generated by the converters do not flow into the ac systems. On the dc side a smoothing inductor  $L_s$  is connected to the output of each converter to smooth the ripples in the dc current; dc filters are also provided to cancel-out harmonics from traveling down the dc transmission line. The direction of the power transfer can be reversed as well by changing the operating principle of the converters.

Figure 1.8 A double-poled Thyristor-Based HVDC Link

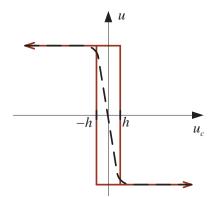

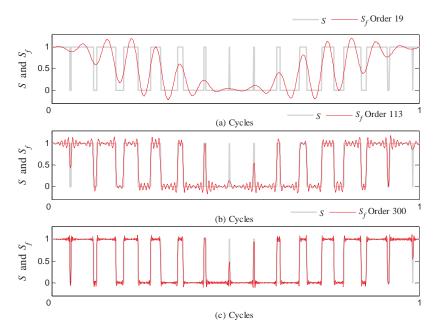

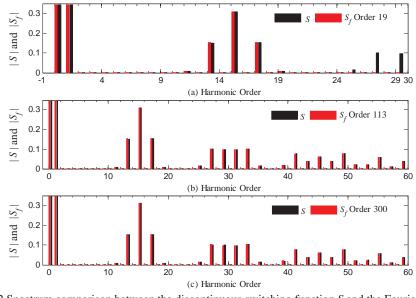

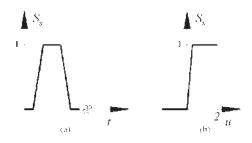

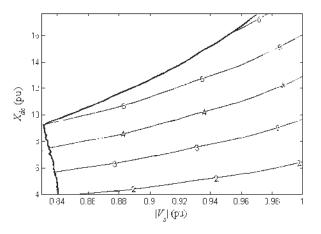

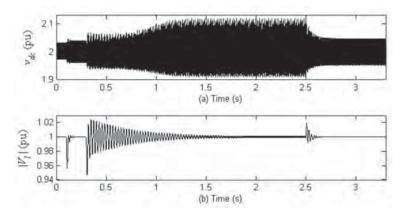

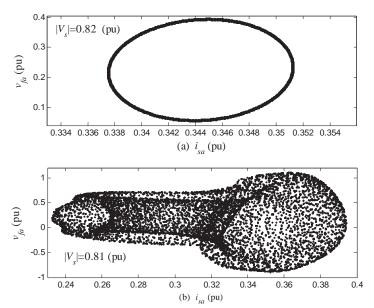

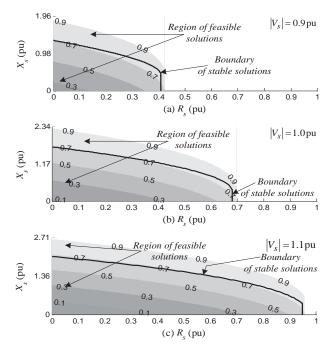

#### 1.1.4.4 High Voltage Direct Current (HVDC) Light